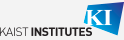

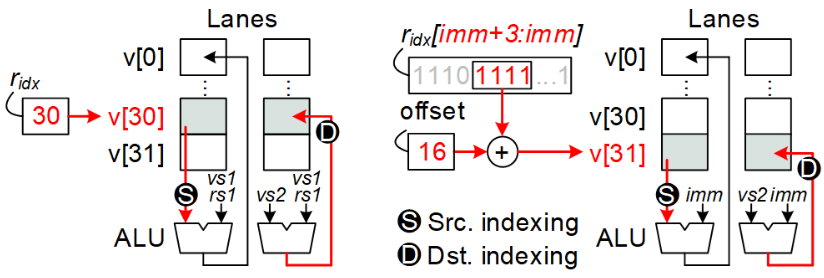

Prof. Wanyeong Jung’s group at KAIST has presented a versatile vertical indexing processor (VVIP) designed for edge computing devices that maximizes the utilization of internal circuits. The single-instruction multiple-data (SIMD)-based VVIP utilizes custom source and destination indexing to activate registers and data-steering logic in the calculations. The proposed indexing method seamlessly integrates arithmetic instructions and transforms address operands into vertical index operands. VVIP reduces the computational overhead incurred by conventional control sequence indexing by directly accessing the register files (RFs) as lookup tables (LUTs) or accumulators through a dynamic index.

VVIP accelerates essential computational tasks, such as bit-serial multiplication and sparse data handling, by incorporating RF indexing into data processing paths. Since it largely reuses the circuits in the original RF, the proposed vertical indexing incurs a minimal, constant overhead that remains unaffected by the degree of parallelism, unlike legacy horizontal indexing instructions.

VVIP is verified on a RISC-V vector processor. It is evaluated using an in-house cycle-accurate simulator, and the hardware area is measured using a 28 nm CMOS process library. It has an area overhead of less than 2.8% and exhibits a 10.1 times average execution speedup on linear algebra benchmarks when compared with the 1-bit-serial multiplication. It also achieves a 1.2-fold average performance enhancement on unstructured (10-90%) sparse pointwise convolution when compared with conventional switch-case statement sequences. Hyungjoon Bae, the first author, stated that the VVIP will bring high computational efficiency to resource-constrained edge devices.

This work was presented at the Design Automation Conference (DAC), held at the Moscone West in San Francisco, USA, on June 22-25, 2024. It also was supported by an Institute of Information & Communications Technology Planning & Evaluation (IITP) grant funded by the Korean government (Ministry of Science and ICT, MSIT) (No.2020-0-01297, Development of Ultra-Low Power Deep Learning Processor Technology using Advanced Data Reuse for Edge Applications).

Hyungjoon Bae (Ph.D. candidate), Prof. Wanyeong Jung School of Electrical Engineering, KAIST

E-mail: jo_on@kaist.ac.kr

Homepage: https://seed.kaist.ac.kr