IMC (In-Memory Computing) refers to a next-generation semiconductor that integrates memory and a processing unit within a single chip. This design addresses the data bottleneck and excessive power consumption issues arising from the conventional computing structure where memory and processors are separated, known as the Von Neumann Architecture.

Although CIM semiconductors were developed in the past, most of them required more than eight transistors for a single memory cell when using SRAM (Static Random Access Memory). Alternatively, if they were based on DRAM (Dynamic Random Access Memory), they utilized a peripheral digital circuit for computation, which was not integrated inside the memory cell array. This approach minimized the distance between memory and the computing unit but did not significantly enhance computation performance.

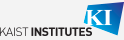

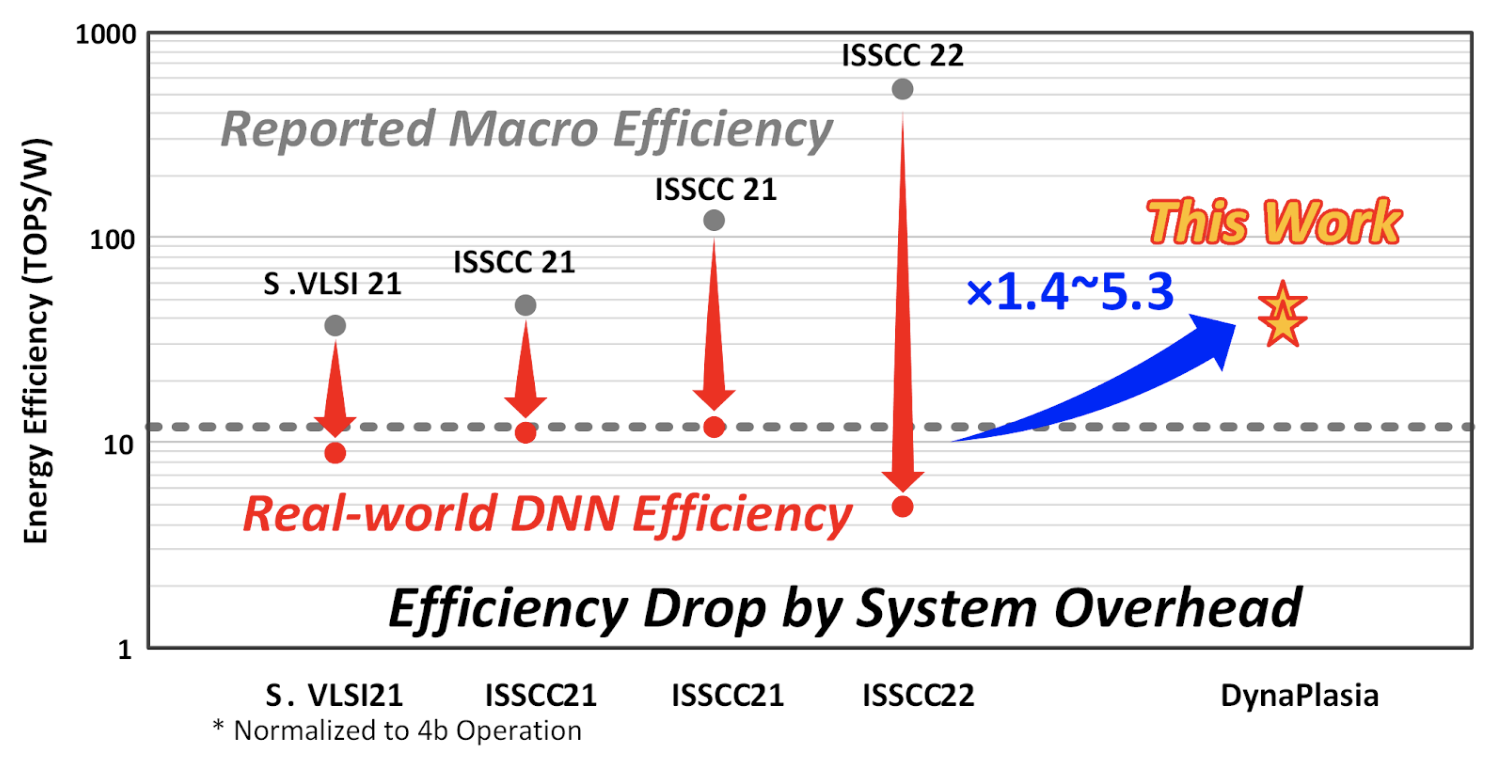

DynaPlasia, as announced by the research team, is an analog DRAM-CIM-based AI semiconductor. It is composed of only three transistors per cell, integrates a processing unit inside the memory cell, and employs analog computing that is highly parallel and energy-efficient, leading to significant improvements in area efficiency and energy efficiency. Moreover, by reducing leakage current from the DRAM, all memory cells can operate in parallel, achieving about 15 times higher throughput compared to conventional digital DRAM-CIM solutions.

Furthermore, while previous analog CIM implementations separately handled memory, processing units, and an ADC with a fixed hardware structure, this research introduced the world’s first ‘triple-mode cell’ capable of simultaneously performing the functions of memory, calculation, and data conversion. As a result, it achieved higher energy efficiency than previous analog CIM semiconductors.

This research was presented at the International Solid-State Circuits Conference (ISSCC) held in San Francisco in February 2023.

Sangjin Kim School of Electrical Engineering, KAIST

E-mail: sangjinkim@kaist.ac.kr

Homepage: http://ssl.kaist.ac.kr