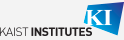

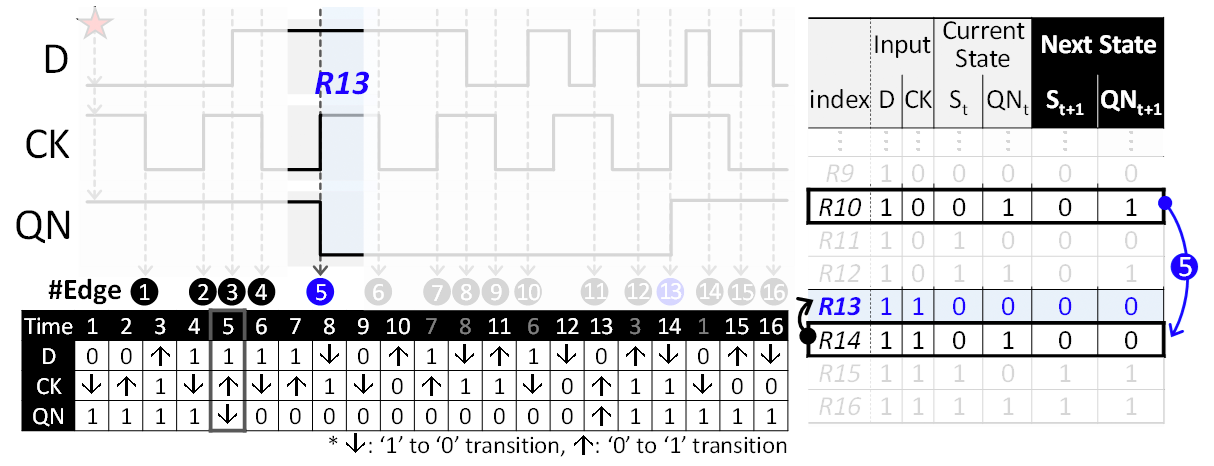

Prof. Wanyeong Jung’s group has developed SeGen, an automatic topology generator for sequencing elements in digital circuits. Traditional design methods often depend on designer expertise and typically explore only a limited subset of flip-flop (FF) topologies. In contrast, SeGen systematically generates all possible Boolean functions that represent sequencing behavior, translates these functions into gate-level descriptions, and ultimately derives optimized transistor-level schematics.

Through an exhaustive search of FF behaviors, SeGen has produced a diverse array of FF architectures, including both conventional master–slave structures and pulsed latches. Furthermore, SeGen enables systematic exploration of sequencing behaviors beyond conventional designs. By exhaustively covering Boolean functions, SeGen has uncovered previously overlooked, efficient topologies that support diverse application needs in power- and speed-sensitive environments. This framework also allows easy extension of the functionality qualification step to generate not only the standard positive-edge-triggered FFs but also other sequencing elements such as toggle FFs and dual-edge-triggered FFs.

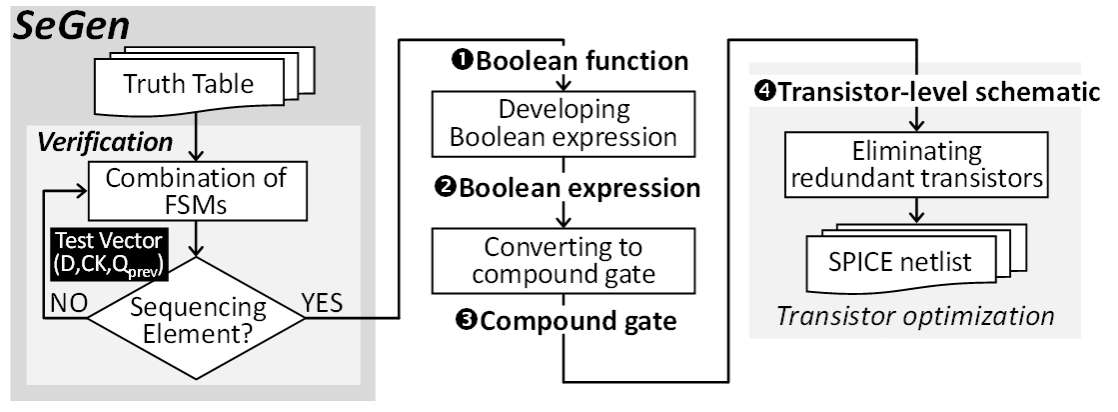

Notably, several novel topologies such as SeGen8 and SeGen28 have demonstrated significant performance gains. These designs exhibit 203%–257% improvements in the energy–delay product compared to traditional transmission-gate flip-flops, all while maintaining minimal area overhead when evaluated under a 65 nm CMOS process.

This work was presented at the ACM International Conference on Computer-Aided Design (ICCAD), held in New York, NY, USA, on October 27–31, 2024. This work was partly supported by an Institute of Information & Communications Technology Planning & Evaluation (IITP) grant funded by the Korean government (MSIT) (No.2020-0-01297, Development of Ultra-Low Power Deep Learning Processor Technology using Advanced Data Reuse for Edge Applications, 50%) and Samsung Electronics Co., Ltd (Contract ID: MEM230315_0004, 50%). The EDA Tool was supported by the IC Design Education Center (IDEC), Korea.

Kyounghun Kang (Ph.D. candidate), Prof. Wanyeong Jung School of Electrical Engineering, KAIST

E-mail: rudgn546@kaist.ac.kr

Homepage: https://seed.kaist.ac.kr